## RM65-7104E

RM 65 Microcomputer Family

**Rockwell**

## RM65-7104E RM 65 ADAPTER/BUFFER FOR AIM 65

### RM 65 MICROCOMPUTER MODULES

RM 65 Microcomputer Module products are designed for OEM and end user microcomputer applications requiring state-of-the-art performance, compact size, modular design and low cost. Software for RM 65 systems can be developed in R6500 Assembly Language, PL/65, BASIC and FORTH. Both BASIC and FORTH are available in ROM and can be incorporated into the user's system.

RM 65 Module products use a motherboard interconnect concept and accept any card in any slot. The 64-line RM 65 Bus offers memory addressing up to 128K bytes, high immunity to electrical noise and includes growth provisions for user functions. A selection of card cages provides packaging flexibility. RM 65 products may also be used with Rockwell's AIM 65 Microcomputer for product development and for a broad variety of portable or desktop microcomputer applications.

### ORDERING INFORMATION

| Part No.   | Description               |

|------------|---------------------------|

| RM65-7104E | Adapter Buffer for AIM 65 |

### FEATURES

- RM 65 Bus Compatible

- Buffered address data and control lines

- Drives up to 15 modules

- Fully assembled, tested and warranted

### PRODUCT OVERVIEW

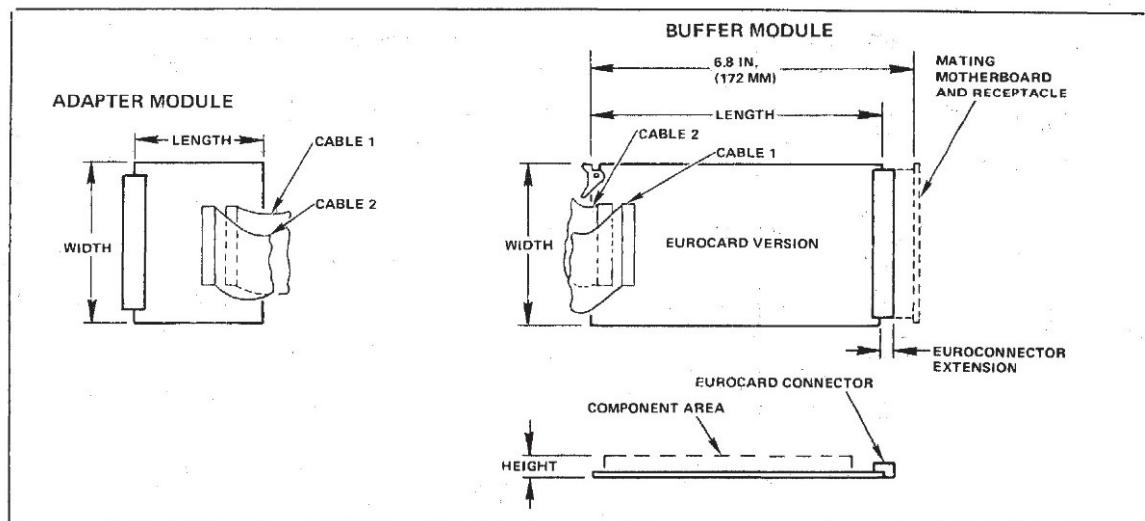

The RM65-7104E Adapter/Buffer extends the AIM 65 Expansion Bus from the AIM 65 Expansion Connector to an RM 65 Bus motherboard that is situated up to 16 inches away. Included circuitry permits the Adapter/Buffer to drive up to 15 RM 65 Bus-compatible modules. (The similar Cable Driver Adapter/Buffer, Part Number RM65-7116, provides the same drive capability for applications in which the motherboard is up to six feet from the Expansion Connector.)

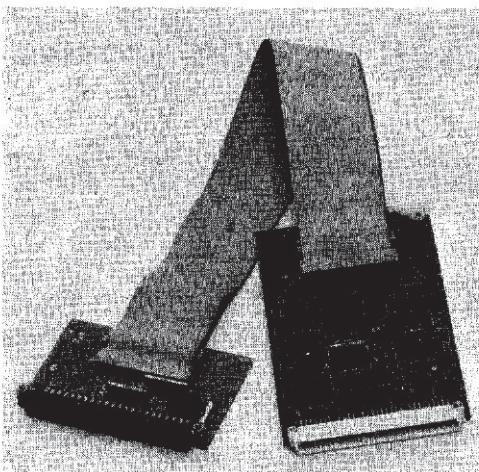

The Adapter/Buffer consists of an adapter module, a buffer module and two 16-inch interconnect cables. Both cables are flexible, so the motherboard may be installed in a wide variety of locations and orientations relative to the AIM 65.

RM65-7104E Adapter/Buffer for AIM 65

## FUNCTIONAL DESCRIPTION

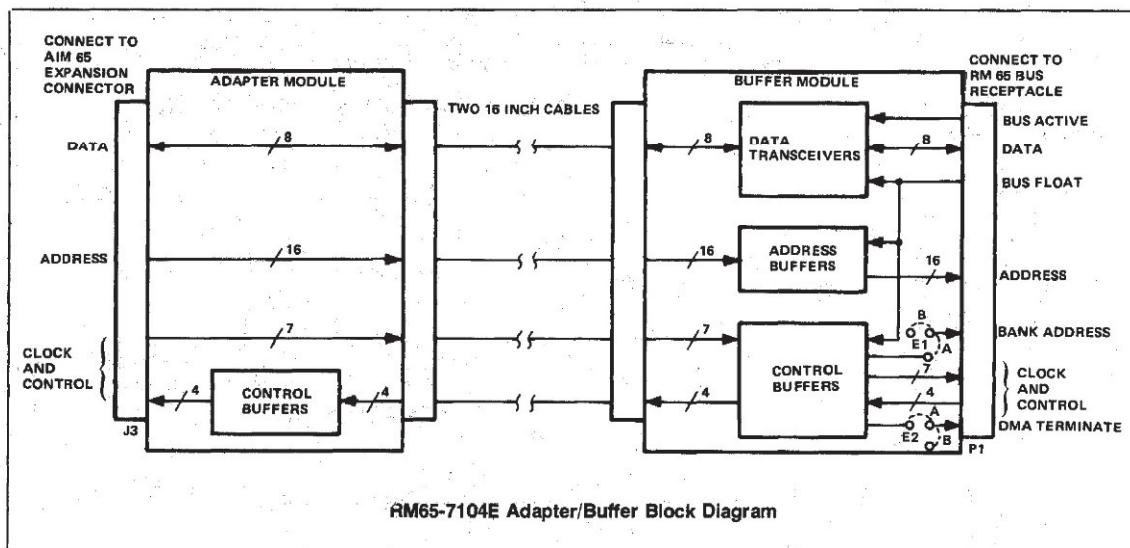

The Adapter/Buffer consists of two modules and two interconnect cables. The Adapter module connects to the AIM 65 Expansion connector and the Buffer module connects to an RM 65 Bus motherboard receptacle.

The Adapter module transfers data, address and control lines from AIM 65 Expansion Connector to the interconnect cables. The eight data and 16 address lines are routed directly, without buffering. The read/write, clock, sync and reset AIM 65 output control lines are also routed directly through the Adapter. The ready, set overflow, interrupt request and non-maskable interrupt AIM 65 input lines are buffered on the module.

Two 16-inch 40 conductor flat ribbon cables connect the Adapter module to the Buffer module. The cables are mass terminated at each end, and are permanently attached to the interfacing module.

The Buffer module buffers and routes all interface signals between the interconnect cables and the RM 65 Bus connector.

The Data Transceivers invert and drive 8-bits of parallel data. During a write operation, data received from the cables are driven onto the RM 65 Bus. During a read operation, data received from the RM 65 Bus are driven onto the cables. The bus active signal enables the Transceivers. When the bus float signal is active, the Transceivers are disabled.

The Address Buffers invert and transfer 16 parallel address lines from the interconnect cable to the RM 65 Bus. When the bus float signal is active, the Buffers are disabled.

Jumper E1 selects the source for the bank address line (BADR)—either the buffer module or an external module. When the buffer module is the source (position A), the bank address line is held high to address Bank 0 (Lower 65K) on the Bus; this line is disabled when the bus float line is active. For an external source (position B), the bank address line is not used by the buffer module, and must be controlled by another module on the Bus.

The seven read/write, clock, sync and reset lines from the cables to the bus are buffered by the Control Drivers. All of these lines, except reset and phase 1, are disabled when the bus float line is active. The ready, set overflow, interrupt request and non-maskable lines from the bus to the interconnect cables are also buffered by the Control Drivers.

Jumper E2 selects the source for the DMA Terminate line (BDMT)—either the buffer module or an external module. When the buffer module is the source (position A), the DMA terminate line is held high (inactive). For an external source (position B), the DMA terminate line is not used by the buffer module, and must be controlled by another module on the bus.

## INSTALLATION/REMOVAL

### Installing the Adapter/Buffer

Before installing the module, inspect for damage and grease, dirt, liquid or other foreign material that will affect performance.

- a. Before installing the Adapter/Buffer, turn off power to the AIM 65 and the interfacing RM 65 Bus motherboard.

- b. Configure Jumpers E1 and E2, per the Functional Description.

- c. Align the Adapter module connector J3 pin 1 with the AIM 65 Expansion Connector J3 pin 1.

- d. Plug the Adapter module onto the Expansion Connector. Press in firmly on the end of module until all pins are securely seated.

- e. Install connector P1 of the Buffer module into the desired slot on the mating RM 65 Bus motherboard.

### CAUTION

RM 65 Bus connectors are keyed to prevent improper module connection. If the module does not insert into the receptacle with moderate pressure applied, check the orientation and connector alignment of the module. Forcing the module improperly into the receptacle may damage the receptacle and/or the module.

- f. Apply power to the AIM 65 and to the mating RM 65 Bus motherboard.

### Removing the Adapter/Buffer

- a. Turn off power to the AIM 65 and to the RM 65 Bus motherboard.

- b. Lift up on the Buffer module ejector tab to release the module from the mating RM 65 Bus receptacle. Pull the module straight back until it is free from the card slot guides.

- c. Pull back on the Adapter module while moving it slightly from side to side until it is free from the AIM 65 Expansion Connector.

| Buffer Module to RM 65 Bus Connector Pin Assignments |                              |              |     |                      |                 |                                  |              |

|------------------------------------------------------|------------------------------|--------------|-----|----------------------|-----------------|----------------------------------|--------------|

| Bottom (Solder Side)                                 |                              |              |     | Top (Component Side) |                 |                                  |              |

| Signal Mnemonic                                      | Signal Name                  | Input/Output | Pin | Pin                  | Signal Mnemonic | Signal Name                      | Input/Output |

| GND                                                  | Ground                       |              | 1a  | 1c                   | +5V             | +5 Vdc                           |              |

| BADR/                                                | Buffered Bank Address        | O            | 2a  | 2c                   | BA15/           | Buffered Address Bit 15          | O            |

| GND                                                  | Ground                       |              | 3a  | 3c                   | BA14/           | Buffered Address Bit 14          | O            |

| BA13/                                                | Buffered Address Bit 13      | O            | 4a  | 4c                   | BA12/           | Buffered Address Bit 12          | O            |

| BA11/                                                | Buffered Address Bit 11      | O            | 5a  | 5c                   | GND             | Ground                           |              |

| BA10/                                                | Buffered Address Bit 10      | O            | 6a  | 6c                   | BA9/            | Buffered Address Bit 9           | O            |

| BA8/                                                 | Buffered Address Bit 8       | O            | 7a  | 7c                   | BA7/            | Buffered Address Bit 7           | O            |

| GND                                                  | Ground                       |              | 8a  | 8c                   | BA6/            | Buffered Address Bit 6           | O            |

| BA5/                                                 | Buffered Address Bit 5       | O            | 9a  | 9c                   | BA4/            | Buffered Address Bit 4           | O            |

| BA3/                                                 | Buffered Address Bit 3       | O            | 10a | 10c                  | GND             | Ground                           |              |

| BA2/                                                 | Buffered Address Bit 2       | O            | 11a | 11c                  | BA1/            | Buffered Address Bit 1           | O            |

| BA0/                                                 | Buffered Address Bit 0       | O            | 12a | 12c                  | B $\phi$ 1      | Buffered Phase 1 Clock           | O            |

| GND                                                  | Ground                       |              | 13a | 13c                  | BSYNC           | Buffered Sync                    | O            |

| BSO                                                  | Buffered Set Overflow        | I            | 14a | 14c                  | BDRQ1/          | *Buffered DMA Request 1          |              |

| BRDY                                                 | Buffered Ready               | I            | 15a | 15c                  | GND             | Ground                           |              |

| +12V/+V                                              | *User Spare 1                |              | 16a | 16c                  | -12V/-V         | *-12 Vdc/-V                      |              |

| GND                                                  | *+12 Vdc/+V                  |              | 17a | 17c                  | BFLT/           | *User Spare 2                    |              |

|                                                      | Ground Line                  |              | 18a | 18c                  | B $\phi$ 0      | Buffered Bus Float               | I            |

| BDMT/                                                | Buffered DMA Terminate       |              | 19a | 19c                  | GND             | *Buffered External Phase 0 Clock |              |

|                                                      | *User Spare 3                |              | 20a | 20c                  | 21c             | Ground                           |              |

| BR/W/                                                | Buffered Read/Write "Not"    | O            | 21a | 21c                  | BDRQ2/          | *Buffered DMA Request 2          |              |

|                                                      | *System Spare                |              | 22a | 22c                  | BR/W            | Buffered Read/Write              | O            |

| GND                                                  | Ground                       |              | 23a | 23c                  | BACT/           | Buffered Bus Active              | I            |

| BIRQ/                                                | Buffered Interrupt Request   |              | 24a | 24c                  | BNMI/           | Buffered Non-Maskable Interrupt  | I            |

| B $\phi$ 2/                                          | Buffered Phase 2 "Not" Clock | O            | 25a | 25c                  | GND             | Ground                           |              |

| B $\phi$ 2                                           | Buffered Phase 2 Clock       | O            | 26a | 26c                  | BRES/           | Buffered Reset                   | O            |

| BD7/                                                 | Buffered Data Bit 7          | I/O          | 27a | 27c                  | BD6/            | Buffered Data Bit 6              | I/O          |

| GND                                                  | Ground                       |              | 28a | 28c                  | BD5/            | Buffered Data Bit 5              | I/O          |

| BD4/                                                 | Buffered Data Bit 4          | I/O          | 29a | 29c                  | BD3/            | Buffered Data Bit 3              | I/O          |

| BD2/                                                 | Buffered Data Bit 2          | I/O          | 30a | 30c                  | GND             | Ground                           |              |

| BD1/                                                 | Buffered Data Bit 1          | I/O          | 31a | 31c                  | BD0/            | Buffered Data Bit 0              | I/O          |

| +5V                                                  | +5 Vdc                       |              | 32a | 32c                  | GND             | Ground                           |              |

## Note

\*Not used on this module.

| Adapter Module to AIM 65 Expansion Connector Pin Assignments |                        |              |                      |     |                 |                      |              |

|--------------------------------------------------------------|------------------------|--------------|----------------------|-----|-----------------|----------------------|--------------|

| Top (Component Side)                                         |                        |              | Bottom (Solder Side) |     |                 |                      |              |

| Signal Mnemonic                                              | Signal Name            | Input/Output | Pin                  | Pin | Signal Mnemonic | Signal Name          | Input/Output |

| SYNC                                                         | SYNC                   | I            | 1                    | A   | A0              | Address Bit 0        | I            |

| RDY                                                          | Ready                  | O            | 2                    | B   | A1              | Address Bit 1        | I            |

| $\phi_1$                                                     | Phase 1 Clock          | I            | 3                    | C   | A2              | Address Bit 2        | I            |

| IRQ                                                          | Interrupt Request      | O            | 4                    | D   | A3              | Address Bit 3        | I            |

| S.O.                                                         | Set Overflow           | O            | 5                    | E   | A4              | Address Bit 4        | I            |

| NMI                                                          | Non-Maskable Interrupt | O            | 6                    | F   | A5              | Address Bit 5        | I            |

| RES                                                          | Reset                  | O            | 7                    | H   | A6              | Address Bit 6        | I            |

| D7                                                           | Data Bit 7             | I/O          | 8                    | J   | A7              | Address Bit 7        | I            |

| D6                                                           | Data Bit 6             | I/O          | 9                    | K   | A8              | Address Bit 8        | I            |

| D5                                                           | Data Bit 5             | I/O          | 10                   | L   | A9              | Address Bit 9        | I            |

| D4                                                           | Data Bit 4             | I/O          | 11                   | M   | A10             | Address Bit 10       | I            |

| D3                                                           | Data Bit 3             | I/O          | 12                   | N   | A11             | Address Bit 11       | I            |

| D2                                                           | Data Bit 2             | I/O          | 13                   | P   | A12             | Address Bit 12       | I            |

| D1                                                           | Data Bit 1             | I/O          | 14                   | R   | A13             | Address Bit 13       | I            |

| D0                                                           | Data Bit 0             | I/O          | 15                   | S   | A14             | Address Bit 14       | I            |

| -12V                                                         | *-12 Vdc               |              | 16                   | T   | A15             | Address Bit 15       | I            |

| +12V                                                         | *+12 Vdc               |              | 17                   | U   | SYS $\phi_2$    | System Phase 2 Clock | I            |

| CS8                                                          | *Chip Select 8         |              | 18                   | V   | SYS R/W         | System Read/Write    | I            |

| CS9                                                          | *Chip Select 9         |              | 19                   | W   | R/W             | Read/Write "Not"     | I            |

| CSA                                                          | *Chip Select A         |              | 20                   | X   | TEST            | *Test                | I            |

| +5V                                                          | +5 Vdc                 |              | 21                   | Y   | $\phi_2$        | Phase 2 Clock "Not"  | I            |

| GND                                                          | Ground                 |              | 22                   | Z   | RAM R/W         | *RAM Read/Write      | I            |

## Note

\* = Not used on this module.

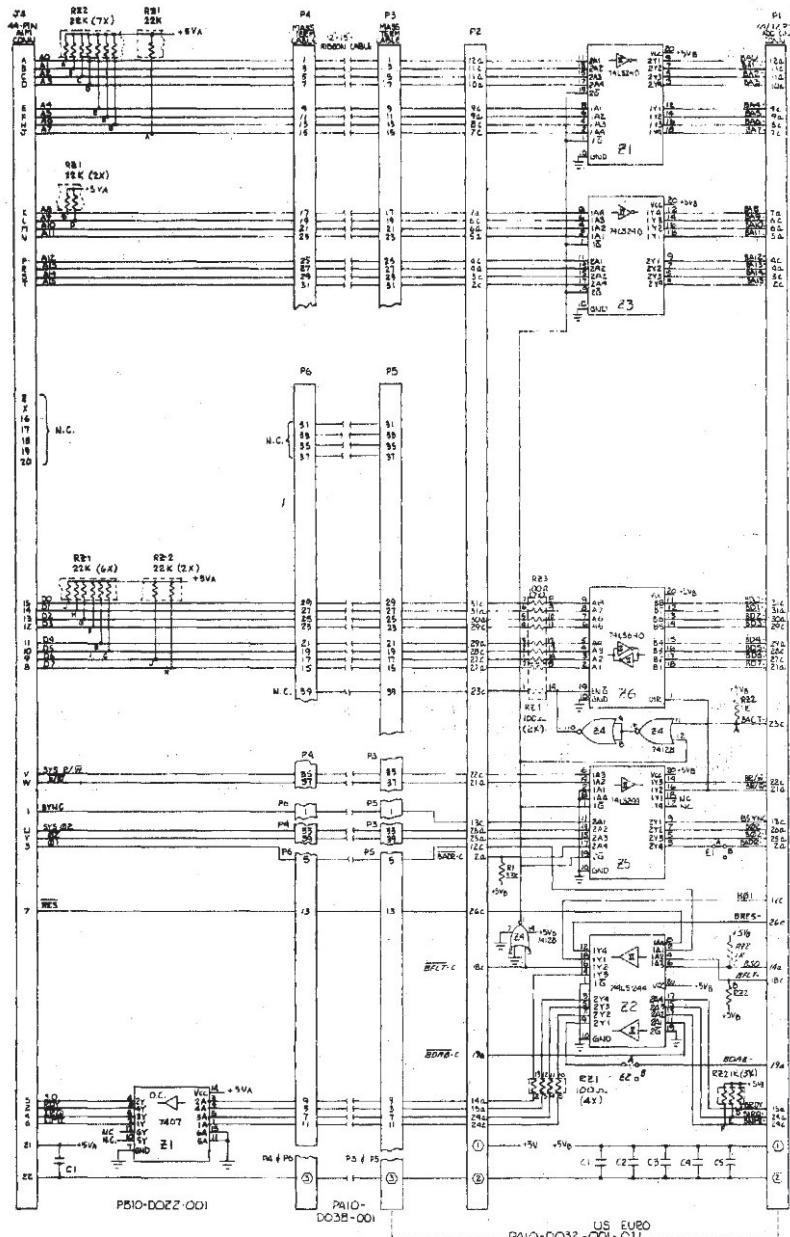

## ADAPTER/BUFFER SCHEMATIC

## SPECIFICATIONS

| Parameter                      | Value                                                                     |

|--------------------------------|---------------------------------------------------------------------------|

| <b>Dimension (See Notes)</b>   |                                                                           |

| Adapter Module                 |                                                                           |

| Width                          | 4.4 in. (111 mm)                                                          |

| Length                         | 2.6 in. (67 mm)                                                           |

| Height                         | 0.56 in. (14 mm)                                                          |

| Buffer Module                  |                                                                           |

| Width                          | 3.9 in. (100 mm)                                                          |

| Length                         | 6.3 in. (160 mm)                                                          |

| Height                         | 0.56 in. (14 mm)                                                          |

| <b>Weight</b>                  | 7.2 oz. (205 g)                                                           |

| <b>Power</b>                   |                                                                           |

| Adapter Module                 | +5V $\pm$ 5% 30 mA (0.15W)—Typical<br>50 mA (0.25W)—Maximum               |

| Buffer Module                  | +5V $\pm$ 5% 190 mA (0.95W)—Typical<br>330 mA (1.7W)—Maximum              |

| <b>Environmental</b>           |                                                                           |

| Operating Temperature          | 0°C to 70°C                                                               |

| Storage Temperature            | -40°C to 85°C                                                             |

| Relative Humidity              | 0% to 85% (without condensation)                                          |

| <b>Propagation Time</b>        | 20 ns—Maximum                                                             |

| <b>Interface Connectors</b>    |                                                                           |

| AIM 65 Expansion Connector     | 22/44—edge receptacle<br>(0.156 in. centers)                              |

| RM 65 Bus                      | 64-pin plug (0.100 in. centers) per DIN 41612<br>(Row b is not installed) |

| <b>Interface Cables</b>        |                                                                           |

| Number of Cables               | Two                                                                       |

| Cable Length                   | 16 inches                                                                 |

| Type                           | Flat ribbon                                                               |

| Number of conductors per cable | 40                                                                        |

| Wire Size                      | #28 AWG                                                                   |

## Notes:

1. The height includes the maximum values for component height above the board surface (0.4 in. for populated modules), printed circuit board thickness (0.062 in.), and pin extension through the bottom of the module (0.1 in.)

2. The length does not include extensions beyond the edge of the module due to the connectors or the module ejector.

3. The Adapter Module dimensions conform to DIN 41612.