# using elbug

It is almost a year since the article on Elbug, the monitor software program for the Elektor SC/MP  $\mu$ P system was published. The original article concentrated on a description of the various control functions which Elbug provided, and did not examine how the program actually worked. Prompted partly by the many requests from readers, the following article takes a more detailed look at Elbug, describing how some of the more important subroutines function, and how these routines can profitably be incorporated into one's own programs.

(H. Huschitt)

## Programming techniques

Writing programs for microcomputers is not difficult, providing one adopts the approach of breaking the program down into a number of smaller units which can be tackled individually. Just as a complex electronic circuit is built up from a number of separate components, so any large program is composed of a number of smaller routines and subroutines. This is also true of Elbug, which contains e.g. a display routine, which ensures that the hexadecimal representation of a data byte appears on the displays, a keyboard routine, which ensures that the correct code is generated when a particular key is depressed, and so on. Subroutines are implemented by jumping from the main program to the start address of the routine in question. At the end of the routine the microprocessor resumes main program execution by jumping back to the address of the main program instruction which follows the subroutine call.

In higher programming languages, such as, e.g. BASIC, there are special instructions, GOSUB (go to subroutine) and RETURN (return from subroutine), for these tasks. Certain microprocessors are also provided with similar instructions, however this is not the case with the SC/MP. The instruction which the SC/MP employs to initiate a subroutine is XPPC (Exchange Pointer with Program Counter). By loading the address of the subroutine in whichever pointer is specified, the above instruction will effect a jump to that routine, since the address in question is loaded into the program counter.

The SC/MP has of course three 16-bit pointer registers in addition to the

program counter. Each of these pointers may be used as page pointers, stack pointers or subroutine pointers, however PTR 3 is unique in that, when the SC/MP senses an interrupt request (the enable interrupt line – Sense bit A in the Status Register – goes high) the SC/MP automatically executes an XPPC-3 instruction. Thus, after a valid interrupt, the next instruction executed will be that contained in the address held in PTR 3 (incremented by one). At the end of the interrupt routine the jump back to the main program is similarly effected by means of an XPPC-3 instruction. As a result of this interrupt facility, PTR 3 is conventionally assigned as the subroutine pointer. However, it is of course perfectly feasible to use the other two pointer registers to call subroutines from within the main program.

To implement a subroutine call, the subroutine pointer is actually loaded with the start address of the routine *minus one*. The reason for this is that the SC/MP increments the contents of the program counter *before* it fetches the next instruction. Thus:

```

LDI L(SUBR)-1

XPAL n

LDI H(SUBR)

XPAH n

```

Since the address contained in the subroutine pointer must be incremented in order to obtain the true start address of the subroutine, it is important that this operation does not require a carry from bit 11 to bit 12 of the address since the SC/MP will not perform such a carry. Thus, for example, if the start address of the subroutine is F000, normally the address loaded into the

Table 1.

|           |                                     |

|-----------|-------------------------------------|

| DELAY:    |                                     |

| LDI 08    | ; load counter with 8               |

| ST COUNT  |                                     |

| LOOP:     |                                     |

| DLY X'FF  |                                     |

| DLD COUNT |                                     |

| JNZ LOOP  | ; execute delay instruction 8 times |

| XPPC 3    | ; jump back to main program         |

| JMP DELAY | ; jump to start                     |

| COUNT:    |                                     |

| • BYTE    | ; RAM byte as counter               |

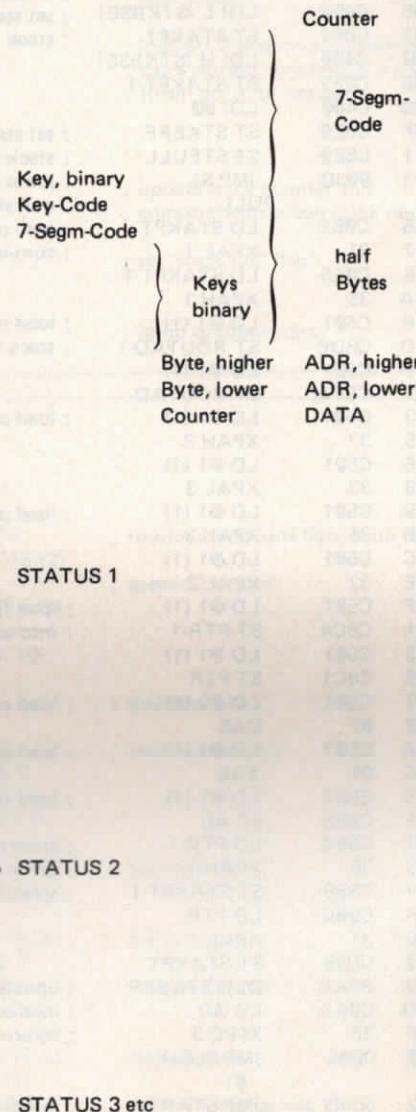

Figure 1. This figure illustrates the functions assigned to the various locations in Elbug's software stack.

1

| ADR  | STACK          | LDKB | GETHEX   | PUTHEX |

|------|----------------|------|----------|--------|

| 0FFF | STAKPT, lower  |      |          |        |

| 0FFE | STAKPT, higher |      |          |        |

| 0FFD | ROUTAD, lower  |      |          |        |

| 0FFC | ROUTAD, higher |      |          |        |

| 0FFB | STFULL         |      |          |        |

| 0FFA | STDEEP         |      |          |        |

| 0FF9 | STKEFF         |      |          |        |

| 0FF8 | AC             |      |          |        |

| 0FF7 | PTR, lower     |      |          |        |

| 0FF6 | PTR, higher    |      |          |        |

| 0FF5 | SPEED          |      |          |        |

| 0FF4 |                |      |          |        |

| 0FF3 |                |      |          |        |

| 0FF2 |                |      |          |        |

| 0FF1 |                |      |          |        |

| 0FF0 |                |      |          |        |

| 0FEF |                |      |          |        |

| 0FEE |                |      |          |        |

| 0FED |                |      |          |        |

| 0FEC |                |      |          |        |

| 0FEB |                |      |          |        |

| 0FEA |                |      |          |        |

| 0FE9 | Key, binary    |      |          |        |

| 0FE8 | Key-Code       |      |          |        |

| 0FE7 | 7-Segm-Code    |      |          |        |

| 0FE6 |                |      |          |        |

| 0FE5 |                |      |          |        |

| 0FE4 |                |      |          |        |

| 0FE3 |                |      |          |        |

| 0FE2 |                |      |          |        |

| 0FE1 |                |      |          |        |

| 0FE0 | STKBSE         |      |          |        |

| 0FD9 | AC             |      |          |        |

| 0FDE | E              |      |          |        |

| 0FDD | SR             |      |          |        |

| 0FDC | PTR 1 L        |      |          |        |

| 0FDB | PTR 1 H        |      |          |        |

| 0FDA | PTR 2 L        |      | STATUS 1 |        |

| 0FD9 | PTR 2 H        |      |          |        |

| 0FD8 | PTR 3 L        |      |          |        |

| 0FD7 | PTR 3 H        |      |          |        |

| 0FD6 | ROUTAD L       |      |          |        |

| 0FD5 | ROUTAD H       |      |          |        |

| 0FD4 | AC             |      |          |        |

| 0FD3 | E              |      |          |        |

| 0FD2 | SR             |      |          |        |

| 0FD1 | PTR 1 L        |      | STATUS 2 |        |

| 0FD0 | PTR 1 H        |      |          |        |

| 0FCF | PTR 2 L        |      |          |        |

| 0FCE | PTR 2 H        |      |          |        |

| 0FCD | PTR 3 L        |      |          |        |

| 0FCC | PTR 3 H        |      |          |        |

| 0FCB | ROUTAD L       |      |          |        |

| 0FCA | ROUTAD H       |      |          |        |

| 0FC9 | AC             |      |          |        |

pointer would be F000 - 1 = EFFF. However in this instance the address thereby obtained would be incorrect, since, as stated, there can be no carry from bit 11 to bit 12 and the four highest address bits would remain unaltered (i.e. 'E'). The correct address to enter into the pointer is therefore FFFF.

Whilst the subroutine is being executed, PTR 3 will contain the address of the last instruction executed in the main program, i.e. the return address -1,

assuming of course that the contents of the PTR are not altered by the subroutine. Thus an XPPC-3 instruction at the end of the subroutine will effect a return to main program execution. However, the address now held by PTR 3 will be that of the last instruction in the subroutine, which means that a subsequent XPPC-3 instruction would effect a jump to the end of the subroutine and not the start. For this reason the final instruction of almost every subroutine will be a jump back to

the start of the routine.

A practical example of the above-described techniques is the delay routine listed in table 1. This routine can be used in the course of main program execution in order to avoid filling a large portion of program memory with delay instructions. If the delay routine is used repetitively, the subroutine call will be structured as follows:

- JS 3\* (DELAY); load PTR 3 and make first jump to delay routine

- XPPC 3 ; second jump to delay routine

- XPPC 3 ; third jump to delay routine

Unfortunately, the process is not quite as simple as might first appear. The contents of the accumulator are altered by the subroutine. Thus if the contents of the AC prior to the jump to delay routine are required later in the main program, they must first be stored somewhere. As long as it is simply the contents of the AC which must be preserved, this does not present any special problems, since they can easily be stored in the extension register. Unfortunately, however, the situation becomes slightly more complicated if the contents of the pointers themselves are altered in the course of a subroutine, since the return addresses to the main program will then be lost.

Thus it is necessary to store the return addresses at the beginning of the subroutine, and then re-enter these into the pointers at the end of the routine, so that an XPPC instruction will effect a return to the main program.

From a programming point of view it is extremely useful to be able to jump from the middle of one subroutine to a second subroutine, i.e. to 'nest' routines inside one another like Chinese boxes. However for each jump that is made a return address must be stored, so that it must be possible to 'stack up' the return addresses somewhere in memory in order that they can be retrieved as required. Some microprocessors are provided with an integral on-chip stack, capable of storing up to 12 or 16 return addresses. This is not the case with the SC/MP, however, so that it is necessary to employ a 'software stack'.

### Software lifo stack

A software stack is basically a routine which simulates the function of a stack

\*JS 3 is a symbol for a 'pseudo instruction', i.e. a statement which results in the generation of several machine-language instructions — in this case the loading of PTR 3 and exchanging the contents of PC and PTR 3.

register, by employing a section of read/write memory as a scratch-pad store for the data to be saved.

The advantage of a software stack is that there need be virtually no limit to its *depth*, i.e. the number of return addresses it is capable of storing. In addition there is the possibility of storing the contents of other important registers, such as the AC or extension register, in the stack. The software stack of Elbug utilises the section of RAM between  $\$FC9$  and  $\$FFF$ . This section was chosen since it can easily be addressed via the program counter from the beginning of that page of memory (i.e. from  $\$0000$ ). In addition to return addresses the contents of all the CPU registers, with the exception of the PC, are stored on Elbug stack.

In order to store the status of all of the CPU registers 11 bytes of RAM are required. Figure 1 indicates which locations are reserved for this purpose. As can be seen, the stack contains sufficient space to store the status of each CPU register twice. Since Elbug only nests to a level of one subroutine (i.e. one subroutine called by another) this is sufficient. However a particular user's program may require several subroutines to be nested, in which case the stack can be extended downwards from  $\$FC9$  as far as is desired.

The stack is organised on a 'last-in-first-out' (lifo) basis, and employs a 'stack pointer' – usually PTR 2 – to point to the last value pushed onto the stack. A 'stack routine' is required to write the contents of the CPU registers into the stack, and in order to ensure that the stack pointer can be used during a subroutine and the stack address still be preserved, the status of the stack pointer (STAKPT) is itself stored in locations  $\$FFF$  and  $\$FFE$  at the top of the stack (see figure 1). When Elbug is started, the address  $\$FE0$  is written into these locations; this location represents the 'base' of the stack. The section of stack from  $\$FFF$  to  $\$FE0$  is fixed, however below this point the stack can be expanded or contracted as required.

In a user's program which contains a large number of nested interrupts, there exists the danger of the dynamic portion of the stack being extended downwards to the point where it overlaps a user's program stored from  $\$C00$  onwards. In order to prevent such an eventuality, a stack counter (STKEFF) is maintained, which is incremented or decremented each time a byte is pushed onto or pulled off the stack. In addition, a byte of RAM is reserved which, via the MODIFY routine or the user's program, can be used to specify the number of bytes of status information which may be stored on the stack.

This byte, which effectively determines the depth of the stack, is stored in location  $\$FFA$  (STDEEP) – see figure 1. This byte is compared with the contents of the stack counter each time a stack operation is performed, and when the effective stack depth (STEFF) equals

Table 2.

## Elbug STACK routines

|      |               |                                             |

|------|---------------|---------------------------------------------|

| 0700 | DISPL = 0700  | ; EA of display                             |

| 0FFF | STAKPT = 0FFF | ; 2 bytes for current contents of stack ptr |

| 0FFD | ROUTAD = 0FFD | ; 2-byte address of subroutine              |

| 0FFB | STFULL = 0FFB | ; 'stack-full' flag                         |

| 0FFA | STDEEP = 0FFA | ; 1 byte to set stack depth                 |

| 0FF9 | STKEFF = 0FF9 | ; current stack depth                       |

| 0FF8 | AC = 0FF8     | ; scratch-pad for (ac)                      |

| 0FF7 | PTR = 0FF7    | ; scratch-pad for (ptr)                     |

| 0FF5 | SPEED = 0FF5  | ; speed of cassette routine                 |

| 0FE0 | STKBSE = 0FE0 | ; stack base                                |

| 0000 | . = 0000      |                                             |

|      | STACK:        |                                             |

| 0000 | 08            | NOP                                         |

| 0001 | C415          | LDI X'15                                    |

| 0003 | C8F1          | ST SPEED                                    |

| 0005 | C4E0          | LDI L (STKBSE)                              |

| 0007 | C8F7          | ST STAKPT                                   |

| 0009 | C40F          | LDI H (STKBSE)                              |

| 000B | C8F2          | ST STAKPT-1                                 |

| 000D | C400          | LDI 00                                      |

| 000F | C8E9          | ST STKEFF                                   |

| 0011 | C8E9          | ST STFULL                                   |

| 0013 | 903D          | JMP \$1                                     |

|      | PULL:         |                                             |

| 0015 | C0E9          | LD STAKPT                                   |

| 0017 | 31            | XPAL 1                                      |

| 0018 | C0E5          | LD STAKPT-1                                 |

| 001A | 35            | XPAH 1                                      |

| 001B | C501          | LD @1 (1)                                   |

| 001D | C8DE          | ST ROUTAD-1                                 |

| 001F | C501          | LD @1 (1)                                   |

| 0021 | C8DB          | ST ROUTAD                                   |

| 0023 | C501          | LD @1 (1)                                   |

| 0025 | 37            | XPAH 3                                      |

| 0026 | C501          | LD @1 (1)                                   |

| 0028 | 33            | XPAL 3                                      |

| 0029 | C501          | LD @1 (1)                                   |

| 002B | 36            | XPAH 2                                      |

| 002C | C501          | LD @1 (1)                                   |

| 002E | 32            | XPAL 2                                      |

| 002F | C501          | LD @1 (1)                                   |

| 0031 | C8C4          | ST PTR-1                                    |

| 0033 | C501          | LD @1 (1)                                   |

| 0035 | C8C1          | ST PTR                                      |

| 0037 | C501          | LD @1 (1)                                   |

| 0039 | 07            | CAS                                         |

| 003A | C501          | LD @1 (1)                                   |

| 003C | 01            | XAE                                         |

| 003D | C501          | LD @1 (1)                                   |

| 003F | C8B8          | ST AC                                       |

| 0041 | C0B4          | LD PTR-1                                    |

| 0043 | 35            | XPAH 1                                      |

| 0044 | C8B9          | ST STAKPT-1                                 |

| 0046 | C0B0          | LD PTR                                      |

| 0048 | 31            | XPAL 1                                      |

| 0049 | C8B5          | ST STAKPT                                   |

| 004B | B8AD          | DLD STKEFF                                  |

| 004D | C0AA          | LD AC                                       |

| 004F | 3F            | XPPC 3                                      |

| 0050 | 9004          | JMP PUSH                                    |

|      | \$1:          |                                             |

| 0052 | 904D          | JMP START                                   |

|      | \$2:          |                                             |

| 0054 | 90BF          | JMP PULL                                    |

|      | PUSH:         |                                             |

| 0056 | C8A1          | ST AC                                       |

| 0058 | C0A6          | LD STAKPT                                   |

| 005A | 33            | XPAL 3                                      |

| 005B | C8B9          | ST PTR                                      |

| 005D | C0A0          | LD STAKPT-1                                 |

| 005F | 37            | XPAH 3                                      |

| 0060 | C895          | ST PTR-1                                    |

| 0062 | C4FF          | LDI L (STAKPT)                              |

| 0064 | 31            | XPAL 1                                      |

| 0065 | CFFC          | ST @-4 (3)                                  |

Table 2, continued.

|      |      |                |                                       |

|------|------|----------------|---------------------------------------|

| 0067 | C40F | LDI h (STAKPT) |                                       |

| 0069 | 35   | XPAH 1         |                                       |

| 006A | CFFF | ST @-1 (3)     |                                       |

| 006C | 01   | XAE            | ; push (e) onto stack                 |

| 006D | CB03 | ST 3 (3)       |                                       |

| 006F | 06   | CSA            | ; push (sr) onto stack                |

| 0070 | CB02 | ST 2 (3)       |                                       |

| 0072 | C1F9 | LD-7 (1)       | ; (ac) from scratch-pad onto stack    |

| 0074 | CB04 | ST 4 (3)       |                                       |

| 0076 | 32   | XPAL 2         | ; push (ptr 2) onto stack             |

| 0077 | CFFF | ST @-1 (3)     |                                       |

| 0079 | 36   | XPAH 2         |                                       |

| 007A | CFFF | ST @-1 (3)     |                                       |

| 007C | C1F8 | LD-8 (1)       | ; (ptr 3) from scratch-pad onto stack |

| 007E | CFFF | ST @-1 (3)     |                                       |

| 0080 | C1F7 | LD-9 (1)       |                                       |

| 0082 | CFFF | ST @-1 (3)     |                                       |

| 0084 | C1FE | LD-2 (1)       | ; routine-address from 'ROUTAD'       |

| 0086 | CFFF | ST @-1 (3)     | ; onto stack                          |

| 0088 | C1FD | LD-3 (1)       |                                       |

| 008A | CFFF | ST @-1 (3)     | ; load ptr 3 with routine address and |

| 008C | 37   | XPAH 3         | ; store current contents of stack ptr |

| 008D | C9FF | ST-1 (1)       | ; (from ptr 3) in 'stakpt'            |

| 008F | C1FE | LD-2 (1)       |                                       |

| 0091 | 33   | XPAL 3         |                                       |

| 0092 | C900 | ST 0 (1)       |                                       |

| 0094 | A9FA | ILD-6 (1)      | ; update stack counter and            |

| 0096 | E1FB | XOR-5 (1)      | ; compare with preset stack depth     |

| 0098 | 9C04 | JNZ \$3        |                                       |

| 009A | C4FF | LDI X'FF       | ; set 'stack-full' flag               |

| 009C | C9FC | ST-4 (1)       |                                       |

|      |      | \$ 3:          |                                       |

| 009E | 3F   | XPPC 3         |                                       |

| 009F | 90B3 | JMP \$2        | ; jump to subroutine                  |

Table 3. LDBYTE routine

|      |      |             |                                         |

|------|------|-------------|-----------------------------------------|

|      |      | .LOCAL      |                                         |

|      |      | .PAGE       |                                         |

|      |      | LDBYTE:     | ; routine: fetch one byte from cassette |

| 01D1 | C215 | LD X'15 (2) |                                         |

| 01D3 | 1C   | SR          |                                         |

| 01D4 | CA14 | ST X'14 (2) |                                         |

|      |      | \$ 1:       |                                         |

| 01D6 | C4FF | LDI X'FF    |                                         |

| 01D8 | 01   | XAE         |                                         |

| 01D9 | 19   | SIO         | ; give stop bit                         |

| 01DA | 40   | LDE         |                                         |

| 01DB | 9402 | JP \$2      |                                         |

| 01DD | 90F7 | JMP \$1     | ; wait for start bit                    |

|      |      | \$ 2:       |                                         |

| 01DF | C4FF | LDI X'FF    |                                         |

| 01E1 | 01   | XAE         |                                         |

| 01E2 | C214 | LD X'14 (2) | ; copy speed/2                          |

| 01E4 | CA0A | ST 10 (2)   |                                         |

|      |      | \$ 3:       |                                         |

| 01E6 | BA0A | DLD 10 (2)  | ; 1/2 bit delay                         |

| 01E8 | 9CFC | JNZ \$3     |                                         |

| 01EA | C408 | LDI 08      | ; load bit-counter                      |

| 01EC | CA08 | ST 8 (2)    |                                         |

|      |      | \$ 4:       |                                         |

| 01EE | C215 | LD X'15 (2) | ; copy speed                            |

| 01F0 | CA09 | ST 9 (2)    |                                         |

| 01F2 | C416 | LDI 22      | ; delay 114 $\mu$ s (sc/mp 1)           |

| 01F4 | 8F00 | DLY 00      |                                         |

|      |      | \$ 5:       |                                         |

| 01F6 | BA09 | DLD 9 (2)   | ; decrement speed                       |

| 01F8 | 9CFC | JNZ \$5     |                                         |

| 01FA | 19   | SIO         | ; accept bit                            |

| 01FB | BA08 | DLD 8 (2)   |                                         |

| 01FD | 9CEF | JNZ \$4     | ; 8 bits accepted                       |

| 01FF | C215 | LD X'15 (2) |                                         |

| 0201 | CA09 | ST 9 (2)    |                                         |

|      |      | \$ 6:       |                                         |

| 0203 | BA09 | DLD 9 (2)   | ; decrement speed (1 x 66 $\mu$ s)      |

| 0205 | 9CFC | JNZ \$6     | ; (sc/mp 1)                             |

| 8207 | 40   | LDE         | ; load byte in ac                       |

| 0208 | 3F   | XPPC 3      | ; return                                |

| 0209 | 90C6 | JMP LDBYTE  | ; jump for next pass                    |

the preset maximum stack depth (STDEEP), this condition is flagged by loading X'FF into 0FFB (=STFULL). The STFULL flag can be tested by the user's program, and if desired set, so that subsequent jumps to subroutine are prevented.

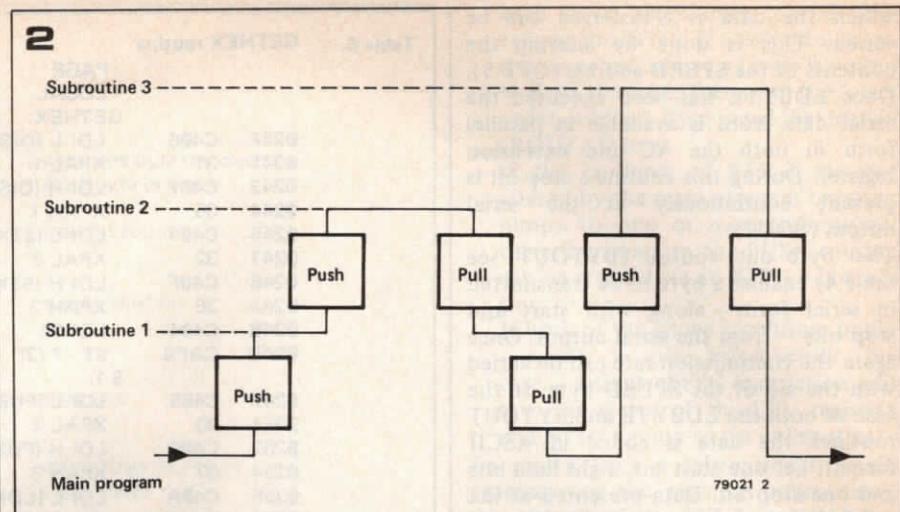

The stack routines in Elbug which are responsible for storing the contents of the CPU registers before a subroutine is executed and retrieving same after the subroutine is finished are designated the PUSH and PULL routines respectively. A complete listing for both routines is provided in table 2, whilst figure 2 illustrates the timing sequence of the routines.

The end of the PUSH routine contains the instructions required to effect the jump to subroutine, thus it is important that the start address of the subroutine in question is first stored on the stack for reference. The 16-bit start address (-1) is loaded into locations 0FFD and 0FFC (ROUTAD).

With the aid of Elbug's stack and the PUSH and PULL routines a jump to subroutine can be implemented as follows:

- the start address (-1) of the subroutine is loaded into the appropriate locations (ROUTAD).

(if the user's program has not yet caused the contents of PTR 2 to be altered, the ROUTAD bytes can be loaded via it. Upon pressing the RUN key and leaving Elbug, PTR 2 is automatically loaded with the address of the stack base (0FEC). The displacement values X'1C and X'1D will reference the higher and lower ROUTAD locations respectively. If PTR 2 has already been used, then effective addresses can be obtained via PTR 3, since the latter will contain the start address (-1) of PUSH. The relative addresses (displacements) are then X'A8 and X'A7 respectively).

- PTR 3 should be loaded with the start address (-1) of the PUSH routine (0055)

- If the above steps have been taken, the actual subroutine jump can be effected by an XPPC-3 instruction.

The program will now jump to PUSH, causing the current contents of the SC/MP's registers to be stored on the stack, whereupon the subroutine will be executed. This subroutine may use any register, the user need have no fears for their original contents. However it is worth noting that it is impossible to transfer data from the main program to a subroutine via one of the CPU registers (and vice versa).

The above procedure will enable a subroutine to be called and implemented under any circumstances. However there are situations where the process is even simpler.

- If the same subroutine is called by the main programme more than once without a second subroutine being called in between, then one need not load the ROUTAD addresses anew

Table 4.

## BYTOUT

| .LOCAL  |      |              |                                |

|---------|------|--------------|--------------------------------|

| BYTOUT: |      |              |                                |

| 05D8    | CA07 | ST 7 (2)     | ; copy one byte to cassette    |

| 05DA    | C40B | LDI 11       | ; store byte in ram            |

| 05DC    | CA08 | ST 8 (2)     | ; load bit-counter             |

| 05DE    | C400 | LDI 00       |                                |

| 05E0    | 01   | XAE          |                                |

| 05E1    | 19   | SIO          | ; supply start bit             |

| 05E2    | 01   | XAE          |                                |

| 05E3    | BA20 | DLD X'20 (2) |                                |

| 05E5    | C207 | LD 7 (2)     |                                |

| 05E7    | 01   | XAE          | ; byte to e                    |

|         |      | \$ 1:        |                                |

| 05E8    | C40B | LDI 11       |                                |

| 05EA    | 8F00 |              | ; delay 70 $\mu$ s (sc/mp 1)   |

| 05EC    | C215 | LD X'15 (2)  | ; copy 'speed'                 |

| 05EE    | CA09 | ST 9 (2)     |                                |

|         |      | \$ 2:        |                                |

| 05F0    | BA09 | DLD 9 (2)    | ; decrement speed              |

| 05F2    | 9CFC | JNZ \$ 2     |                                |

| 05F4    | 19   | SIO          | ; shift bit out                |

| 05F5    | 40   | LDE          |                                |

| 05F6    | DC80 | ORI X'80     | ; add stop bit to byte         |

| 05F8    | 01   | XAE          |                                |

| 05F9    | BA08 | DLD 8 (2)    |                                |

| 05FB    | 9CEB | JNZ \$ 1     | ; if bit-counter = 0, continue |

| 05FD    | 3F   | XPPC 3       | ; return                       |

| 05FE    | 90D8 | JMP BYTOUT   | ; jump for next pass           |

Table 5.

## LDKB routine

| .PAGE  |      |                |                                         |

|--------|------|----------------|-----------------------------------------|

| .LOCAL |      |                |                                         |

| LDKB:  |      |                |                                         |

|        |      |                |                                         |

| 020B   | C414 | LDI L(PULL)-1  | ; prepare ptr 3                         |

| 020D   | 33   | XPAL 3         |                                         |

| 020E   | C400 | LDI H(PULL)    |                                         |

| 0210   | 37   | XPAH 3         |                                         |

|        |      | LDKB1:         | ; label for start address without stack |

| 0211   | C401 | LDI L(DISPL)+1 |                                         |

| 0213   | 31   | XPAL 1         |                                         |

| 0214   | C407 | LDI H(DISPL)   | ; prepare ptr 1 and ptr 2               |

| 0216   | 35   | XPAH 1         |                                         |

| 0217   | C4E0 | LDI L(STKBSE)  |                                         |

| 0219   | 32   | XPAL 2         |                                         |

| 021A   | C40F | LDI H(STKBSE)  |                                         |

| 021C   | 36   | XPAH 2         |                                         |

|        |      | \$ 1:          |                                         |

| 021D   | C108 | LD 8 (1)       |                                         |

| 021F   | 94FC | JP \$ 1        | ; wait for key closure                  |

| 0221   | 8F1E | DLY 30         | ; debounce time – approx. 30 ms         |

| 0223   | C108 | LD 8 (1)       |                                         |

| 0225   | CA08 | ST 8 (2)       | ; store keyboard code in ram            |

| 0227   | D40F | ANI 0F         |                                         |

| 0229   | CA09 | ST 9 (2)       | ; store binary value of key in ram and  |

| 022B   | 01   | XAE            | ; in e                                  |

|        |      | \$ 2:          |                                         |

| 022C   | C108 | LD 8 (1)       |                                         |

| 022E   | 9402 | JP \$ 3        | ; wait for key release                  |

| 0230   | 90FA | JMP \$ 2       |                                         |

|        |      | \$ 3:          |                                         |

| 0232   | 8F1E | DLY 30         | ; debounce time                         |

| 0234   | C41F | LDI L (TAB)    |                                         |

| 0236   | 31   | XPAL 1         |                                         |

| 0237   | C401 | LDI H (TAB)    |                                         |

| 0239   | 35   | XPAH 1         |                                         |

| 023A   | C180 | LD - 128(1)    | ; fetch 7-segment code                  |

| 023C   | CA07 | ST 7 (2)       | ; store in ram                          |

| 023E   | 3F   | XPPC 3         | ; return                                |

each time, since once loaded they remain unaltered. If a second subroutine is called whose address is within  $\frac{1}{4}$  K of the first, then only the lower order address byte need be loaded (ROUTAD low).

- If the contents of PTR 3 are not altered by the main program between jumps to one or more subroutine, then the jump to the PUSH routine can be realised via an XPPC 3 instruction.

- If both of the above conditions apply – which is not infrequently the case – a single XPPC instruction will save the status of the CPU registers and effect a jump to the subroutine!

To return from a subroutine to main program (or the previous subroutine), the address of the PULL routine (start address 0013) is loaded into PTR 3 at the end of the routine in question. If the subroutine does not alter the contents of PTR 3 (again, this will often be the case), the latter will contain the last instruction of the PUSH routine. Since this is in fact a jump to the start address of the PULL routine (see table 2), a single XPPC 3 instruction at the end of the subroutine will cause a return to the main program.

A similar instruction is present at the end of the PULL routine, namely JMP PUSH. This means once PTR 3 has been loaded with the start address (-1) of PUSH, and assuming its contents are not affected by the subroutine, then jumps to and from the subroutine can always be implemented using just an XPPC 3 instruction. The subroutine procedure described above remains valid for external subroutine calls, i.e. interrupt requests. It goes without saying, however, that the interrupt line is not enabled until the ROUTAD bytes and PTR 3 have been loaded. Only then will the XPPC 3 instruction generated by the interrupt cause a jump to subroutine to be implemented.

If several interrupt inputs are used, the software required to recognise the priority of simultaneous interrupt requests must be included in the subroutine. This software was discussed in an earlier article in the SC/MP series (see Elektor 33, January 1977).

## Series/parallel and parallel/series conversion routines

Via the extension register and the SIO (Serial Input/Output) instruction the SC/MP offers the user the possibility of serial/parallel and parallel/serial conversion without the need for additional hardware. The appropriate routines are already contained in Elbug, since they are required when transferring data to and from the cassette interface.

The 'load byte' routine (LDBYTE, see table 3) will load a serial data byte, including start and stop bits, via the serial input (SIN) into the extension register. As was explained in part 5 of the series on the SC/MP system (see Elektor 35, March 1978), the rate at

which the data is transferred can be varied. This is done by altering the contents of the SPEED-address (OFF 5). Once LDBYTE has been executed the serial data word is available in parallel form in both the AC and extension register. During this routine a stop bit is present continuously at the serial output (SOUT).

The 'byte out' routine (BYTOUT, see table 4) enables a byte to be transmitted in serial form – along with start and stop bits – from the serial output. Once again the transmission rate can be varied with the aid of the SPEED byte. In the case of both the LDBYTE and BYTOUT routines the data is coded in ASCII format, i.e. one start bit, eight data bits and one stop bit. Data presented at the serial input during execution of the BYTOUT routine is ignored, which means that using these routines the SC/MP may only be operated in the half-duplex mode.

The routines can be employed in a variety of applications such as, e.g. to interface to a TTY or telex. The routines are initiated not by the Elbug stack routines, but in the manner illustrated in the case of the delay routine described earlier. The user thus has the possibility of inputting and outputting information via the CPU registers. In the case of the BYTOUT routine it is in fact necessary that the byte to be transmitted be loaded into the AC under main program control.

In addition to PTR 3, which is used in jumping to both routines, PTR 2 is also required. Before the jump to either routine this pointer is loaded with  $\emptyset\text{FE}\emptyset$ , since it is via this pointer that the SPEED byte is referenced. Both routines leave PTR 1 unaltered.

### The keyboard routine

This routine, the listing for which is given in table 5, is designed to scan the keyboard. An interesting feature of the routine is that it has two start addresses: LDKB =  $\emptyset\text{20B}$  the start address when called by the stack routines LDKB1 =  $\emptyset\text{211}$  the start address when called by other than the stack routines.

In the latter case PTR 3 is loaded with the address (-1) LDKB1, and the routine started by an XPPC 3 instruction. PTR 3 must be loaded with the appropriate address prior to each jump, since there is no JMP LDKB1 instruction. In both cases the jump back to the main routine is only implemented after the key has been released.

When called by other than via the stack, at the end of the keyboard routine the binary equivalent of the hex data key which has been pressed is available in the extension register, whilst the corresponding 7-segment code is present in the AC. The code generated by the keyboard hardware is written into address  $\emptyset\text{FE8}$ .

If the routine is called via the stack, then it is not possible to transfer infor-

Table 6. GETHEX routine

|      |      |                             |                                      |

|------|------|-----------------------------|--------------------------------------|

|      |      |                             | • PAGE                               |

|      |      |                             | • LOCAL                              |

|      |      |                             | GETHEX:                              |

| 023F | C406 | LDI L (DISPL)+6             | ; load ptr 1 with address            |

| 0241 | 31   | XPAL 1                      | ; of display 6                       |

| 0242 | C407 | LDI H (DISPL)               |                                      |

| 0244 | 35   | XPAH 1                      |                                      |

| 0245 | C4E7 | LDI L (STKBSE)+7            | ; load ptr 2 with                    |

| 0247 | 32   | XPAL 2                      | ; stack base + 7                     |

| 0248 | C40F | LDI H (STKBSE)              |                                      |

| 024A | 36   | XPAH 2                      |                                      |

| 024B | C404 | LDI $\emptyset\text{04}$    | ; load key-counter                   |

| 024D | CAF9 | ST - 7 (2)                  |                                      |

|      |      | \$ 1:                       |                                      |

| 024F | C455 | LDI L (PUSH)-1              |                                      |

| 0251 | 33   | XPAL 3                      |                                      |

| 0252 | C400 | LDI H (PUSH)                |                                      |

| 0254 | 37   | XPAH 3                      |                                      |

| 0255 | C40A | LDI L (LDKB)-1              |                                      |

| 0257 | CBA8 | ST - 88 (3)                 |                                      |

| 0259 | C402 | LDI H (LDKB)                |                                      |

| 025B | CBA7 | ST - 89 (3)                 |                                      |

| 025D | 3F   | XPPC 3                      | ; call 'ldkb' (via stack)            |

| 025E | C4E0 | LDI L (STKBSE)              |                                      |

| 0260 | 33   | XPAL 3                      | ; ptr 3 becomes ram pointer          |

| 0261 | C40F | LDI H (STKBSE)              |                                      |

| 0263 | 37   | XPAH 3                      |                                      |

| 0264 | C307 | LD 7 (3)                    | ; fetch 7-segment code               |

| 0266 | CDFF | ST @-1 (1)                  | ; write to display 5 (4, 3, 2)       |

| 0268 | C400 | LDI $\emptyset\text{00}$    |                                      |

| 026A | C9FF | ST - 1 (1)                  | ; blank all other displays           |

| 026C | C9FE | ST - 2 (1)                  |                                      |

| 026E | C9FD | ST - 3 (1)                  |                                      |

| 0270 | C9FC | ST - 4 (1)                  |                                      |

| 0272 | C9FB | ST - 5 (1)                  |                                      |

| 0274 | C309 | LD 9 (3)                    | ; binary value of key to ram table   |

| 0276 | CEFF | ST @-1 (2)                  |                                      |

| 0278 | BB00 | DLD $\emptyset\text{0}$ (3) |                                      |

| 027A | 9CD3 | JNZ \$ 1                    | ; 4 keys?                            |

| 027C | C480 | LDI X'80                    |                                      |

| 027E | C9FF | ST - 1 (1)                  | ; '*' to displays 0,1                |

| 0280 | C9FE | ST - 2 (1)                  |                                      |

| 0282 | C306 | LD 6 (3)                    | ; form higher byte                   |

| 0284 | 1E   | RR                          |                                      |

| 0285 | 1E   | RR                          |                                      |

| 0286 | 1E   | RR                          |                                      |

| 0287 | 1E   | RR                          |                                      |

| 0288 | 01   | XAE                         |                                      |

| 0289 | C305 | LD 5 (3)                    |                                      |

| 028B | 58   | ORE                         |                                      |

| 028C | CB02 | ST 2 (3)                    |                                      |

| 028E | C304 | LD 4 (3)                    | ; form lower byte                    |

| 0290 | 1E   | RR                          |                                      |

| 0291 | 1E   | RR                          |                                      |

| 0292 | 1E   | RR                          |                                      |

| 0293 | 1E   | RR                          |                                      |

| 0294 | 01   | XAE                         |                                      |

| 0295 | C303 | LD 3 (3)                    |                                      |

| 0297 | 58   | ORE                         |                                      |

| 0298 | CB01 | ST 1 (3)                    |                                      |

|      |      | JSPULL:                     | ; assist-label for return via 'pull' |

| 029A | C400 | JS 3 (PULL)                 | ; to main program                    |

| 029C | 37   |                             |                                      |

| 029D | C414 |                             |                                      |

| 029F | 33   |                             |                                      |

| 02A0 | 3F   |                             |                                      |

mation out of the keyboard routine, via the SC/MP registers, into the main program. The above information is only available at the RAM locations reserved for this purpose, namely  $\emptyset\text{FE7}$  to  $\emptyset\text{FE9}$  (see figure 1). If desired, the table of 7-segment code can be used separately. For organisational reasons it is not included in LDKB, but is stored in memory from location  $\emptyset\text{11F}$ .

### The GETHEX routine

This routine itself calls the above-

described LDKB routine four times in order to store the four hexadecimal numbers successively generated by the keyboard. These four digits are joined together to form two bytes, which are stored at addresses  $\emptyset\text{FE1}$  (lower byte) and  $\emptyset\text{FE2}$  (higher byte). The start address of the GETHEX routine is  $\emptyset\text{23F}$  (see table 6) and the routine is initiated via the stack routines. In order to jump to the routine from the main program the start address (-1) is loaded into location ROUTAD, and

Figure 2. This diagram shows the sequence in which the PUSH and PULL routines of Elbug store and retrieve status information when subroutines are called.

Table 7.

**PUTHEX routine**

```

• PAGE          ; puthex routine

• LOCAL

PUTHEX:

02A1 C4E0    LDI L (STKBSE)

02A3 33      XPAL 3          ; load ptr 3 as ram pointer

02A4 C40F    LDI H (STKBSE)

02A6 37      XPAH 3

02A7 C4E0    LDI L (STKBSE)

02A9 32      XPAL 2          ; prepare ptr 2 and ptr 1 for

02AA C40F    LDI H (STKBSE) ; auto-indexed addressing

02AC 36      XPAH 2

02AD C4E3    LDI L (STKBSE)+3

02AF 31      XPAL 1

02B0 C40F    LDI H (STKBSE)

02B2 35      XPAH 1

02B3 C403    LDI 03          ; load byte-counter

02B5 CB0F    ST 0F (3)

$ 1:

02B7 C200    LD 0 (2)        ; fetch first (next) byte

02B9 D40F    ANI 0F          ; bits 0 - 3 to

02BB CD01    ST @-1 (1)      ; ram

02BD C601    LD @-1 (2)        ; fetch same byte again,

02BF 1C      SR              ; and bits 4-7

02C0 1C      SR

02C1 1C      SR

02C2 1C      SR

02C3 CD01    ST @-1 (1)        ; to next ram address

02C5 BB0F    DLD 0F (3)

02C7 9CEE    JNZ $ 1          ; 3rd byte stored?

02C9 C41F    LDI L (TAB)-1

02CB 31      XPAL 1          ; prepare ptr 1 for indirect addressing

02CC C401    LDI H (TAB)

02CE 35      XPAH 1

02CF C406    LDI 06          ; load hex-character-counter

02D1 CB0F    ST 0F (3)

$ 2:

02D3 C601    LD @-1 (2)        ; fetch first (next) half-byte

02D5 01      XAE

02D6 C180    LD - 128 (1)      ; fetch 7-segment code

02D8 CA05    ST 5 (2)          ; load in ram

02DA BB0F    DLD 0F (3)

02DC 9CF5    JNZ $ 2          ; 6 digits ready?

02DE C400    LDI L (DISPL)

02E0 31      XPAL 1          ; load ptr 1 with address of displays

02E1 C407    LDI H (DISPL)

02E3 35      XPAH 1

02E4 C406    LDI 06          ; load counter

02E6 CB0F    ST 0F (3)

$ 3:

02E8 C601    LD @-1 (2)        ; 7-segment code to

02EA CD01    ST @-1 (1)      ; display 5

02EC BB0F    DLD 0F (3)

02EE 9CF8    JNZ $ 3          ; ready?

02F0 90A8    JMP JSPULL      ; via assist-label to 'pull'

```

PTR 3 is loaded with the start address (-1) of the PUSH routine, whereupon an XPPC 3 can be executed.

When the routine is finished, the two above-mentioned bytes can be read out of their locations in memory (0FE1 and 0FE2) to be used later in the program. Care should be taken to ensure that the data is retrieved before the GETHEX routine is called again, otherwise two new bytes will be written into these locations and the previous data will be lost.

**PUTHEX routine**

The last routine to be examined is also the simplest. The PUTHEX routine does nothing more than convert the contents of memory locations 0FE0 to 0FE2 into the equivalent 7-segment code, and then display the results as a six-digit hexadecimal number. The code for the four lowest-order bits of address 0FE0 appears on display 2 (third from the right), the code for the next four bits on display 3, and so on. The start address of PUTHEX is 02A1 (see table 7), and the routine may only be called via the PUSH routine in the fashion described above.

That concludes the discussion of Elbug routines which can be called by a user's program. As one might have imagined, the entire monitor program has not been analysed, since the remaining routines cannot be used outside of Elbug. It is hoped that the above article will not only reveal how the routines which have been discussed can be profitably incorporated into one's own programs, but also that studying these routines will lead the aspiring programmer to an understanding of the various techniques involved, and enable him to tackle longer and more sophisticated programming tasks. ■