### ROM/PROM PROGRAMMING INSTRUCTIONS

#### B. 2708/2704 Family

Initially, and after each erasure, all bits of the 2708/2704 are in the "1" state (Output High). Information is introduced by selectively programming "0" into the desired bit locations. A programmed "0" can only be changed to a "1" by UV erasure.

The circuit is set up for programming operation by raising the  $\overline{\text{CS}}/\text{WE}$  input (Pin 20) to +12V. The word address is selected in the same manner as in the read mode. Data to be programmed are presented, 8-bits in parallel, to the data output lines (O<sub>1</sub>-O<sub>8</sub>). Logic levels for address and data lines and the supply voltages are the same as for the read mode. After address and data set up one program pulse per address is applied to the program input (Pin 18). One pass through all addresses is defined as a program loop. The number of loops (N) required is a function of the program pulse width ( $t_{PW}$ ) according to N x  $t_{PW} \ge 100$  ms.

The width of the program pulse is from 0.1 to 1 ms. The number of loops (N) is from a minimum of 100 ( $t_{PW}$  = 1 ms) to greater than 1000 ( $t_{PW}$  = 0.1 ms). There must be N successive loops through all 1024 addresses. It is not permitted to apply N program pulses to an address and then change to the next address to be programmed. Caution should be observed regarding the end of a program sequence. The  $\overline{CS}$ /WE falling edge transition must occur before the first address transition when changing from a program to a read cycle. The program pin should also be pulled down to  $V_{ILP}$  with an active instead of a passive device. This pin will source a small amount of current ( $I_{IPL}$ ) when  $\overline{CS}$ /WE is at  $V_{IHW}$  (12V) and the program pulse is at  $V_{ILP}$ .

#### Programming Examples (Using N x t<sub>PW</sub> ≥ 100 ms)

Example 1: All 8096 bits are to be programmed with a 0.5 ms program pulse width.

The minimum number of program loops is 200. One program loop consists of words 0 to 1023.

Example 2: Words 0 to 100 and 500 to 600 are to be programmed. All other bits are "don't care". The program pulse width is 0.75 ms.

The minimum number of program loops is 133. One program loop consists of words 0 to 1023. The data entered into the "don't care" bits should be all 1's.

Example 3: Same requirements as example 2 but the PROM is now to be *updated* to include data for words 750 to 770.

The minimum number of program loops is 133. One program loop consists of words 0 to 1023. The data entered into the "don't care" bits should be all 1's. Addresses 0 to 100 and 500 to 600 must be re-programmed with their original data pattern.

### **ROM/PROM PROGRAMMING INSTRUCTIONS**

# 2704, 2708 PROGRAM CHARACTERISTICS

$T_A = 25^{\circ}$ C,  $V_{CC} = 5$ V  $\pm 5$ %,  $V_{DD} = +12$ V  $\pm 5$ %,  $V_{BB} = -5$ V  $\pm 5$ %,  $V_{SS} = 0$ V, Unless Otherwise Noted.

## **D.C. Programming Characteristics**

| Symbol           | Parameter                                   | Min.            | Тур. | Max.               | Units | Test Conditions                                |

|------------------|---------------------------------------------|-----------------|------|--------------------|-------|------------------------------------------------|

| ILI              | Address and CS/WE Input Sink Current        |                 |      | 10                 | μΑ    | V <sub>IN</sub> = 5.25V                        |

| I <sub>IPL</sub> | Program Pulse Source Current                |                 |      | 3                  | mA    |                                                |

| I <sub>IPH</sub> | Program Pulse Sink Current                  |                 |      | 20                 | mA    |                                                |

| l <sub>DD</sub>  | V <sub>DD</sub> Supply Current              |                 | 50   | 65                 | mA    | Worst Case Supply Currents                     |

| Icc              | V <sub>CC</sub> Supply Current              |                 | 6    | 10                 | mA    | All Inputs High                                |

| I <sub>BB</sub>  | V <sub>BB</sub> Supply Current              |                 | 30   | 45                 | mA    | $\overline{CS}/WE = 5V; T_A = 0^{\circ}C$      |

| VIL              | Input Low Level (except Program)            | V <sub>SS</sub> |      | 0.65               | V     |                                                |

| VIH              | Input High Level for all Addresses and Data | 3.0             |      | V <sub>CC</sub> +1 | V     |                                                |

| V <sub>IHW</sub> | CS/WE Input High Level                      | 11.4            | ,    | 12.6               | ٧     | Referenced to V <sub>SS</sub>                  |

| V <sub>IHP</sub> | Program Pulse High Level                    | 25              |      | 27                 | V     | Referenced to V <sub>SS</sub>                  |

| VILP             | Program Pulse Low Level                     | V <sub>SS</sub> |      | 1                  | V     | V <sub>IHP</sub> - V <sub>ILP</sub> = 25V min. |

## **A.C. Programming Characteristics**

| Symbol           | Parameter                           | Min. | Тур. | Max. | Units |

|------------------|-------------------------------------|------|------|------|-------|

| t <sub>AS</sub>  | Address Setup Time                  | 10   |      |      | μς    |

| tcss             | CS/WE Setup Time                    | 10   | ,    |      | μς    |

| t <sub>DS</sub>  | Data Setup Time                     | 10   |      |      | μς    |

| t <sub>AH</sub>  | Address Hold Time                   | 1    |      |      | μs    |

| tcH              | CS/WE Hold Time                     | .5   |      |      | μs    |

| t <sub>DH</sub>  | Data Hold Time                      | 1    |      |      | μς    |

| t <sub>DF</sub>  | Chip Deselect to Output Float Delay | 0    |      | 120  | ns    |

| t <sub>DPR</sub> | Program To Read Delay               |      |      | 10   | μs    |

| t <sub>PW</sub>  | Program Pulse Width                 | .1   |      | 1.0  | ms    |

| t <sub>PR</sub>  | Program Pulse Rise Time             | .5   |      | 2.0  | μs    |

| tpF              | Program Pulse Fall Time             | .5   |      | 2.0  | μs    |

NOTE: Intel's standard product warranty applies only to devices programmed to specifications described herein.

### **ROM/PROM PROGRAMMING INSTRUCTIONS**

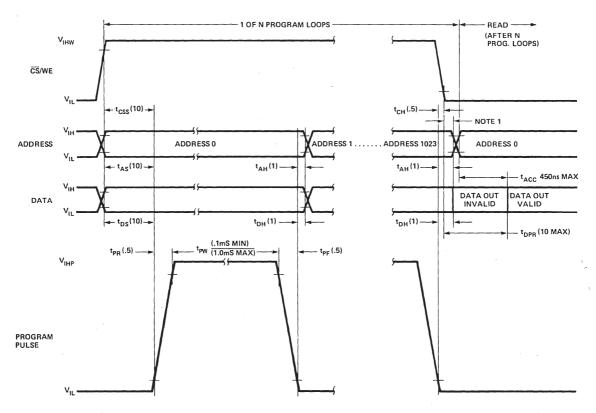

# 2704, 2708 Programming Waveforms

NOTE 1. THE  $\overline{\text{CS}}\textsc{Me}$  transition must occur after the program pulse transition and before the address transition.

NOTE 2. NUMBERS IN ( ) INDICATE MINIMUM TIMING IN  $\mu\text{S}$  UNLESS OTHERWISE SPECIFIED.